Paris-based digital-signal–processing (DSP) IP startup Vsora has introduced a family of PetaFLOPS computational companion chips to accelerate Level 3 (L3) through Level 5 (L5) autonomous-vehicle (AV) designs. Vsora has just raised $4.2 million in a pre-Series B round of financing to hasten its development.

The Tyr chip family uses Vsora’s AD1028 architecture, which combines DSP and deep-learning-accelerator (DLA) units. Tyr is claimed to deliver between 258 trillion and 1,032 trillion operations per second (TOPS) and to consume 10 W.

“In January 2022, we introduced a family of scalable algorithmic accelerator designs based on our Vsora architecture that combines AI in the form of DLA with DSP exchanging data via on-chip memory,” Khaled Maalej, CEO of Vsora, told EE Times Europe. “The combination of AI with DSP is necessary to address Level 4 and Level 5 autonomous driving [AD]. The accelerators, fully programmable in real time in the field, are deployed as companion chips to the main processor, making them relevant to a range of applications, not limited to AD.”

The Tyr family is now composed of three chips: Tyr1, Tyr2 and Tyr3. Maalej said the difference lies in the absolute compute power provided. “This is due to the number of AI and DSP elements encompassed in the respective chip. The larger the number, the more processing power with moderate increase in power consumption, but virtually the same utilization factor and the same latency.”

The silicon is underway, and Vsora is working with partners to roll out the commercial products. It expects to complete an additional round of financing toward the end of the process.

When asked if Vsora is already working on Tyr4 and Tyr5, Maalej said, the architecture is scalable. However, “the algorithm development is happening very fast, so we are always looking to ensure that our solutions are future-proof. Fewer and fewer of today’s suppliers are able to handle the new, advanced algorithms. We are one of the few, and we are very focused on remaining so.”

In its latest “Microprocessor Report,” The Linley Group compared the Tyr1 with the Nvidia Orin and the Qualcomm AI 100 and concluded:

Vsora’s advantage is the impressive efficiency of its architecture. At 30 TOPS/W, the DLA core outperforms all competing IP, including Ceva’s NeuPro-M. Thus, we’d expect it to excel compared with other DLA processors, and Tyr’s initial ResNet-50 numbers are impressive. Nvidia and Qualcomm, however, are experienced chip companies that know how to optimize an SoC design. Vsora may lose some of its advantage if the components around the DLA are inefficient. Until it receives and tests the initial silicon, we won’t know whether the company can meet its aggressive power target.

The company said it plans to make some “major” announcements within the next few months.

ADAS and AD

At this year’s Consumer Electronics Show, the automotive design ecosystem—mainly car OEMs, Tier 1s, semiconductor suppliers and software developers—put advanced driver-assistance system (ADAS) technology in the spotlight.

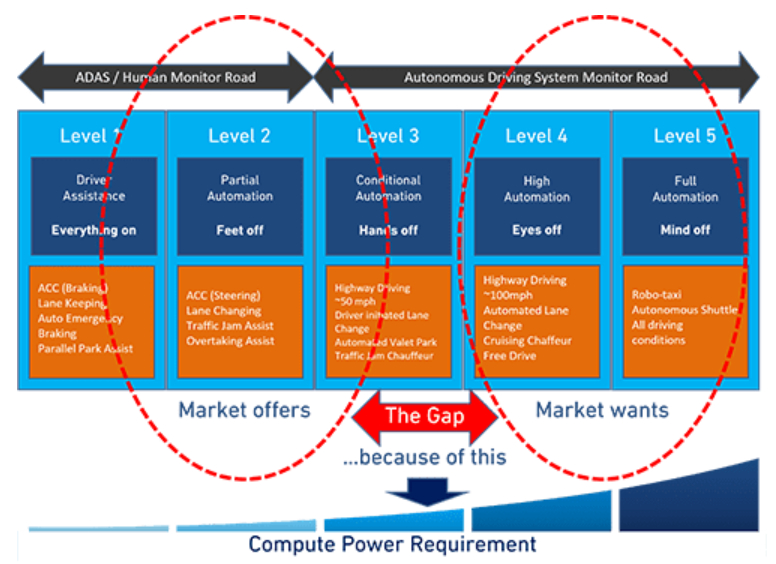

For Maalej, the year 2023 will not be just about ADAS, which comprises all capabilities covered by Level 1 and Level 2+. He said, “What is even more exciting is AD, from L3 to L5.”

Vsora expects to support this trend with its Tyr family, which Maalej describes as “the most advanced algorithmic accelerator for mobile and edge applications” that “excels in processing power delivery at low energy consumption and at affordable prices.”

In the “Microprocessor Report,” The Linley Group indicated:

Vsora’s architecture features both AI and DSP engines connected to a large SRAM that facilitates rapid data sharing. The company believes this approach is critical for AVs, which must perform both functions—sometimes in the same algorithm. Most AV designers, however, seem willing to split AI and DSP between two separate chips. For those that want a single-chip solution, Qualcomm’s AI 100 accelerator also checks all the boxes, although it lags [behind] Tyr in performance.

In his discussions with early customers, Maalej noted an increasing interest in a new generation of algorithms that requires “not just AI but a combination of AI and DSP.” He commented, “As the market gets better at understanding what is necessary for autonomous driving, the algorithms are updated to reflect this. At the same time, we are seeing more sensors with a higher precision that expand exponentially the amount of data generated, and that still has to be processed in the same limited available time.”

Led by Otium Capital and existing investors, the round of financing will be used to accelerate the development of the Tyr family and expand the company’s software and hardware teams to support customers’ needs.

“We started to grow our R&D team at the end of last year, and at the end of 2022, we counted 12 engineers,” Maalej said. “We are accelerating the hiring for 2023 and, in parallel, we are also working with key partners to optimize our resources.”

He continued, “Our R&D [department] spent significant time and brainpower to implement a software-oriented design flow. Programming a Tyr is entirely performed at the high level via a choice of Matlab-like/Tensorflow-like/C++. The Vsora compiler handles the programming code transparently to the user, separating what runs off the main processor from what runs on the Tyr. This accelerates the task, and it simplifies the design and debug flow. The software is continuously enhanced, and part of the funding will be used to keep this trend.”

The company was founded by Maalej and three other ex-DiBcom engineers in September 2015. Vsora’s product development was self-financed with loan support from Bpifrance, France’s public sector innovation financing agency.

In 2018, the startup secured $1.7 million in a Series A round of financing from capital firms Omnes Capital and Partech Ventures and angel investors. The money was used to expand Vsora’s R&D and build sales channels in the U.S. and in Asia.