Project teams designing complex switches and routers have turned to hardware emulation as the foundation for their verification strategy to battle network congestion and outages.

Source: EETimes

Project teams designing complex switches and routers have turned to hardware emulation as the foundation for their verification strategy to battle network congestion and outages.

We consumers are needy — the three billion or so of us who use electronic devices want on-demand access to download emails, texts, videos, and all other forms of communications fast and (often) at the same time. It’s little wonder, then, that networking switch and router designs have become some of the most complex of all chip designs as their sizes and complexities push north of five-hundred million ASIC-equivalent gates.

It is an axiom that the more complex the chip, the more difficult verification becomes because of all the paths that need to be verified. With embedded software nowadays implementing more and more chip functionality, thorough chip verification and validation is getting out of control. In the network domain, efficiency is critical for higher bandwidth, lower latency, and fewer network failures. Collisions are to be avoided at all costs.

In the past, verification engineers extended simulation runs on networking designs to reach convergence on the range of various configurations. While simulation is still useful at the block level, verification of a design with five-hundred million gates with simulated traffic is impractical. Ethernet switches and routers expanding from 256 to 1,024 ports and ramping throughput to 120 Gbps render simulation inadequate.

Instead, project teams debugging system-on-chip (SoC) designs for the network have turned to hardware emulation because this practical tool offers high performance, advanced debug capabilities, and power and performance analysis, all of which goes to reduce time to market and improve quality. A key feature of hardware emulation is its ability to test a design with real traffic.

A modern emulator enables the creation of a block-level to system-level accelerated verification flow for networking to be deployed in datacenters instead of labs by replacing traditional physical devices in the In-circuit Emulation (ICE) mode with virtual devices. Virtualization moves emulation from the engineering lab to the computing datacenter for maximum utilization of emulation resources. In a flash, the various project teams working remotely on that complex networking chip have access to the most versatile verification tool.

Comparing ICE to a virtual approach

With ICE, a single user tasked with verifying a design of a 128-port Ethernet interface and a variable bandwidth of 1/10/40/100/120 Gbps would require one Ethernet tester per port. Since a direct connection is not possible because of the different speed domains between tester and emulated design under test (DUT), a speed rate adapter would be inserted between the two. The setup would include 128 Ethernet testers and 128 Ethernet speed adapters. The sheer size of this physical setup would be mindboggling, not to mention expensive and unreliable.

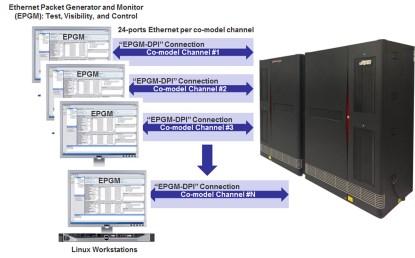

A virtual approach would model the Ethernet testers in software running under Linux on a workstation connected to the emulator. The model would be an accurate representation of the physical tester based on implementation intellectual property (IP). An example is Mentor Graphics’ VirtuaLAB for Ethernet applications. Called Ethernet Packet Generator and Monitor (EPGM), this generates, transmits, and monitors Ethernet packets with the DUT, and it configures GMII, XGMII, XLGMII/CGMII and CXGMII interfaces for 1G, 10G, 40G/100G and 120G. The software performs off-line analysis of the traffic, provides statistics, and supports several other functions.

(Source: Mentor Graphics)

The interface between the virtual tester and the DUT consists of one instance of the SystemVerilog Direct Programming Interface (DPI) communicating to a Virtual Ethernet extended Register Transfer Level (xRTL) transactor hooked up to a Null-PHY, connected to the DUT. One xRTL transactor is required for each port of any xMII-supported type.

Moreover, the virtual approach can support multiple users concurrently to become an enterprise-wide emulation resource.

Project teams designing complex switches and routers have turned to hardware emulation as the foundation for their verification strategy to battle network congestion and outages. They are finding a practical solution that serves the entire enterprise and keeps us demanding consumers satisfied.

Dr. Lauro Rizzatti is a verification consultant and industry expert on hardware emulation. Previously, Dr. Rizzatti held positions in management, product marketing, technical marketing, and engineering. He can be reached at lauro@rizzatti.com.