Marrying high-performance hardware with “smart” applications will make emulators workhorses for addressing complex system-level design verification challenges

Source: EETimes

DVCon, a conference for design and verification engineers, kicks off next week in San Jose, California. At this conference, hardware emulation will be a much-discussed topic in the program and in hallway conversations.

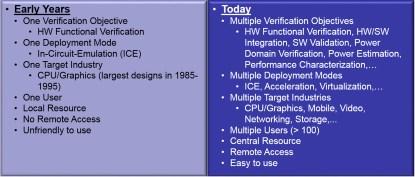

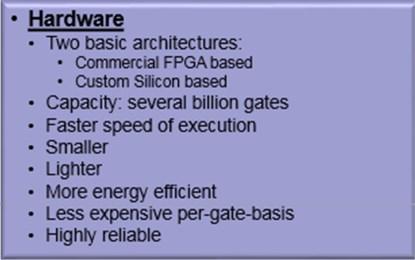

After three decades of somewhat slow, but steady, progress in hardware emulation technology, its future looks bright for accelerated advancements and expectations of new developments. Over the past 30 years, hardware emulators have evolved both in terms of hardware and the supporting software. A quick scan through hardware specifications of a typical emulator of the late 1980s compared with today’s best-in-class reveals that improvements of several characteristics have reached a factor of about 1,000 times.

We can look at the supporting software from two perspectives — the compiler angle and the run-time executable viewpoint.

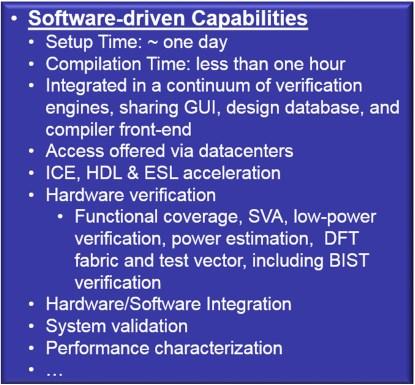

One way to measure the progress in compiler technology is to compare the average setup time of the design-under-test (DUT) in the early days versus today. When they were first introduced, emulators required six months or more to setup a DUT for emulation. It now takes less than one week. While not a 1,000X improvement, this is in the ball park of 50 to 100 times faster, which is still significant.

More difficult or complex to quantify is the progress in run-time software. But a quick glance at the differences in capabilities of emulators in the same period of time reveals dramatic enhancements.

What, then, should we expect in the future? Again, let’s separate the hardware from the software. From the hardware standpoint, emulation vendors will launch new generations of verification engines boasting higher capacity, faster execution, and quicker compilation speed. In fact, one of them has already released one of these next-generation emulators.

It will be interesting to see how the three basic architectures proposed by the three major emulation vendors will hold up and evolve. At the time of this writing, however, such a comparison is not yet possible.

From the software perspective, we will see new deployment modes, starting with the inclusion of the emulation engine in a continuum of verification engines, all sharing a common design database, a common user interface (GUI), and a common compiler front-end. For the record, the compiler front-end includes the hardware description language (HDL) parser and elaborator along with the synthesis that generates the DUT gate-level netlist. Only the first two stages will be shared; not the synthesis portion, since this applies only to hardware-based verification engines, such as emulators and FPGA-based prototypes.

Similarly, the partitioner and the place-and-route portion of the compiler back-end will only be shared among the hardware engines (emulators and FPGA-based prototypes). They are not applicable to software-based verification algorithms, such as HDL simulators, electronic system level (ESL) simulators, and formal analysis.

New applications will be introduced. Examples are support for design for testability (DFT) — namely the ability to verify the gate-level DFT fabric — and to verify test vectors as well as built-in-self-test (BIST) vectors. The use of emulation for performance characterization of new designs will become mainstream, and new ways to validate embedded software will be devised.

An interesting twist already has been implemented by one of the vendors. It architected run-time software as an operating system to accommodate applications (“apps”) similar to the approach taken with smartphones. Also, the trend to move large emulation systems into datacenters that started few years ago will be accelerated. Multiuser capability will be offered by all vendors to increase the return on investment (ROI) of the machines.

The future of emulation is marrying high-performance hardware with “smart” applications that make an emulator a workhorse for addressing complex system-level design verification challenges.

DVCon attendees can expect some substantial announcements from hardware emulation vendors who are exhibiting. I’m looking forward to it, and I will report on this news in my next column.

Dr. Lauro Rizzatti is a verification consultant and industry expert on hardware emulation (www.rizzatti.com). Previously, Dr. Rizzatti held positions in management, product marketing, technical marketing, and engineering. He can be reached at lauro@rizzatti.com.