One of the consequences of the IoT is an increase in the number of Ethernet ports.

Source: Semiconductor Engineering

The enormous growth of the Internet of things (IoT) has an enormous impact on network providers. After all, without the underlying network infrastructure, there would be no IoT. One consequence has been a significant increase in the number of Ethernet ports on networking devices.

Today, Ethernet switches and routers reach 256 ports (by year’s end that number will increase to 1024 ports), and they can handle throughputs of up to 120 Gb/s. Meanwhile, latency in networking switches has constantly decreased, with the lowest latencies drop below 1 µs. These factors combine to make today’s network switches and routers among the largest IC designs ever developed, reaching beyond a half billion gates. Verification of such complex IC designs before silicon availability is a daunting task. Let’s consider the design of an SoC with a 128-port Ethernet interface.

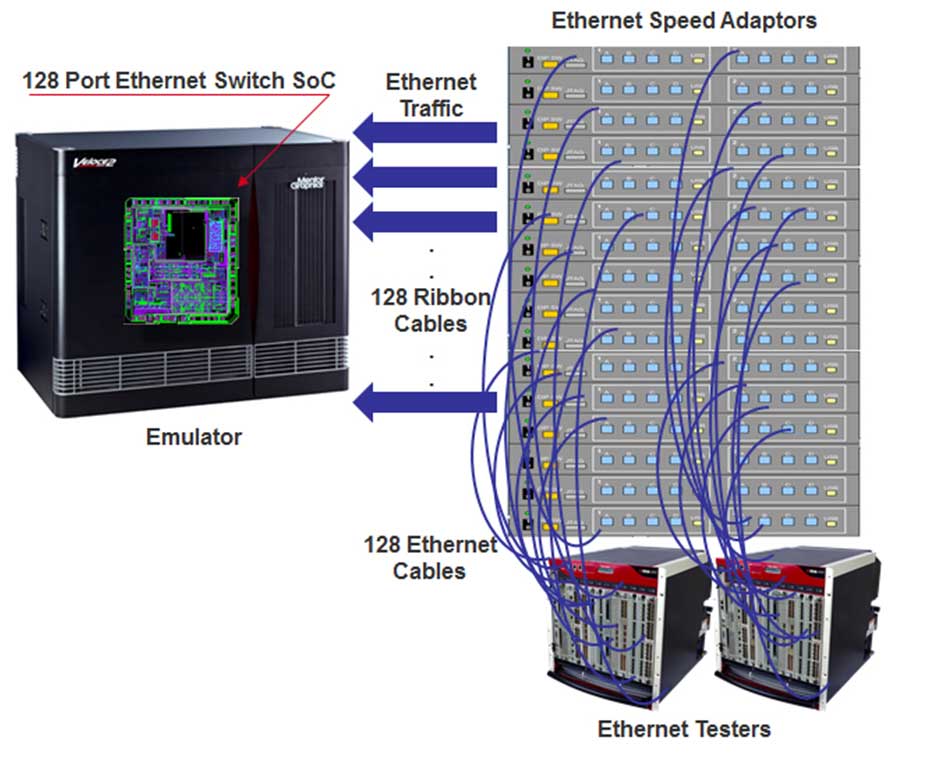

While HDL simulation can be used at the block level, verifying the entire design of several hundred million gates with simulated traffic is unrealistic, and must be ruled out. This is a primary case for using hardware emulation in in-circuit-emulation (ICE) mode. However, an ICE configuration requires one Ethernet tester per port. Since a direct connection is not possible due to the different speed domains between tester and emulated DUT, a speed rate adapter is inserted between the two.

For example, the test setup for our 128-port design requires 128 Ethernet testers and 128 Ethernet speed adapters and all of the cables to connect them (Fig. 1). Apart from the spaghetti-cable arrangement, the potential unreliability of the hardware, and the overall cost, the entire setup supports only a single user who must work in the same building, or room, as the emulation lab. Remote access would be impractical, since it would require manned supervision for managing multiple users with different setups.

This limitation in the context of protocol stimulus modeling became apparent a few years back, creating the need for a software-controlled environment for generating, transmitting, and analyzing Ethernet packets to test Ethernet SoCs mapped inside an emulation platform. With simulation, you can typically verify 1,000 packets per day, whereas emulation can handle over 11 million per day.

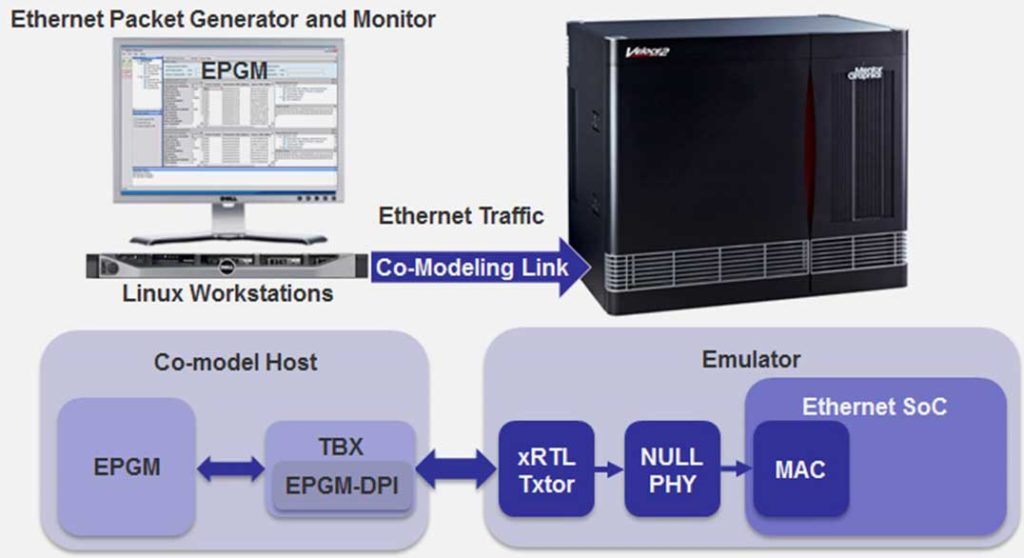

In this scenario, the Ethernet testers are modeled in software running on Linux using a workstation connected to the emulator. The model is an accurate representation of the actual physical tester, based on proven implementation IP. The virtual tester includes an Ethernet Packet Generator and Monitor (EPGM) that has the ability to configure GMII, XGMII, XLGMII/CGMII, and CXGMII interfaces for 1G, 10G, 40G/100G, and 120G respectively. One xRTL transactor is required for each port of any xMII-supported type (Fig. 2).

Multiple tester applications can be bundled together across multiple workstations—known as a multi-co-model—to support large port count configurations. High-speed link (HSL) cards are used to connect co-model channels from workstations to the emulator. This tightly integrated transport mechanism is under the hood, tuned for maximum wall clock performance, and is transparent to the testbench. Data-plane emulation throughput scales linearly with the port count because of this parallel runtime and debug architecture.

This approach yields several other benefits, as well. First, reconfiguring the virtual tester to perform various functions is fast via remote access. Second, the workstation is a stable and reliable piece of equipment acquired at a fraction of the cost of a complex Ethernet tester of equivalent functionality. Even more important is the ability to support multi-concurrent users, essential in backing up a large software-development team. Last, but not least, an emulation datacenter can be used as an enterprise-wide emulation resource.

This also works for complex test-scenario generation and monitoring. An interactive and batch-mode TCL command interface is used to control all MACs and generate a myriad of protocols and traffic flows. Percentages of traffic per protocol type can be mixed with differing packet sizes or random size per flow. Packet-transmission arbitration includes multiple algorithms, such as WRR, DWRR, SO, and Random.

It also allows stress testing and error injection for complex switching topology. Protocol and performance violations are reported. Packets can be reviewed in interactive or batch sessions to examine packet statistics, Tx/Rx trace, metadata, time stamps, and all content on the wire.

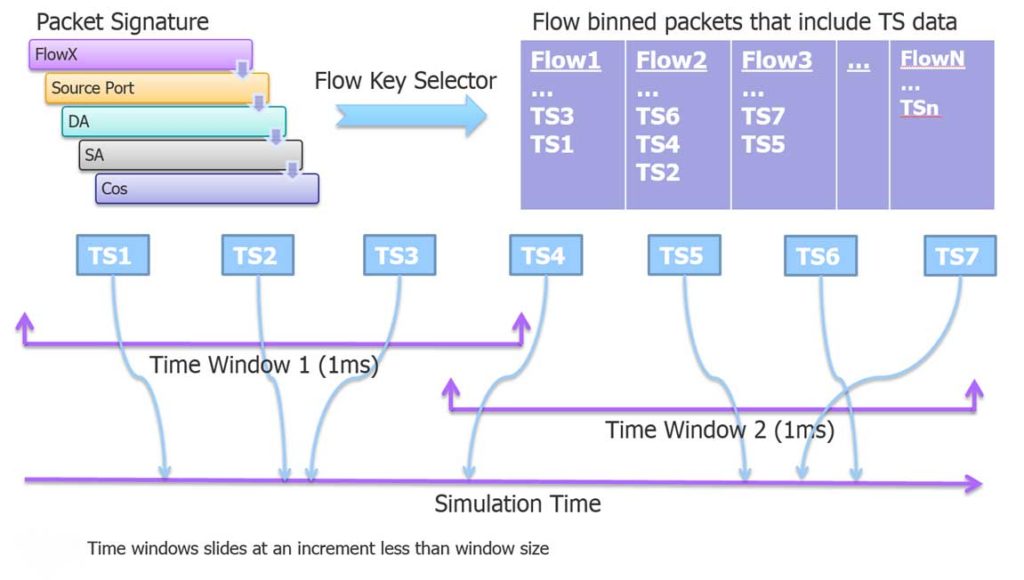

One of the hallmarks of emulation is its ability to do complex performance analysis of large and deep state-full systems. In some cases, millions of packets may be needed to hit steady-state analysis points of interest in the design. Take, for example, measuring bit rates for traffic flows in a terabyte Ethernet switch. Virtual Ethernet signature generation and packet time stamps (TS) are used to calculate these measurements.

Measurements such as these per port per flow can easily consume a week to extract in simulation for large port-count devices. In emulation, these same measurements can be performed within an hour.

To learn more about Mentor Graphics’ approach to these issues, using its VirtuaLAB Ethernet solution, download the free whitepaper Accelerating Networking Products to Market Using Ethernet VirtuaLAB.