Source: Evaluation Engineering

Design for testability (DFT), a way to build testability into an integrated circuit (IC) at the design stage to lower testing costs and increase manufacturing yield, has been around for many years in several different forms. These methodologies—ad-hoc and structured—are able to effectively detect all faults in a circuit, reducing cost and time associated with test development, as well as the execution time of testing fabricated chips.

Scan and MBIST, two of the more popular DFT tools, are inserted in the design after it has been functionally verified. These tools are well worth the price because the cost of testing a large quantity of chips after manufacturing to determine which parts are manufacturing defect free can be as much as 40% of the cost of building the chip. They also can eliminate the risk of passing a failing device that eventually will be caught in the field at a cost much higher than on the manufacturing floor. Obviously, this dramatically impacts profits.

However, inserting an on-chip test infrastructure, such as scan chain, MBIST structure, and compression/decompression logic, can interfere with the chip’s functional correctness. Gate-level verification of the design after the DFT implant is essential at this point. However, today’s design sizes reaching into the multiple hundreds of million gates utterly defeat the performance of hardware description language (HDL) simulation, making it virtually useless for the task at hand.

Only hardware emulation can verify the chip functionality, regardless of its size and complexity. Emulation performs at orders of magnitude faster speed than simulation. For example, approximately three months of simulating a design can be accomplished in a few hours in emulation.

A new DFT “app” is available for hardware emulation* to carry out the daunting task of testing a DFT-implanted design-under-test (DUT) within the allocated schedule that may not allow for any additional time slack outside the already constrained timeframe. It brings two changes to the deployment process of a hardware emulator. The first is a change in the compilation flow, and the second is a change in the run-time execution.

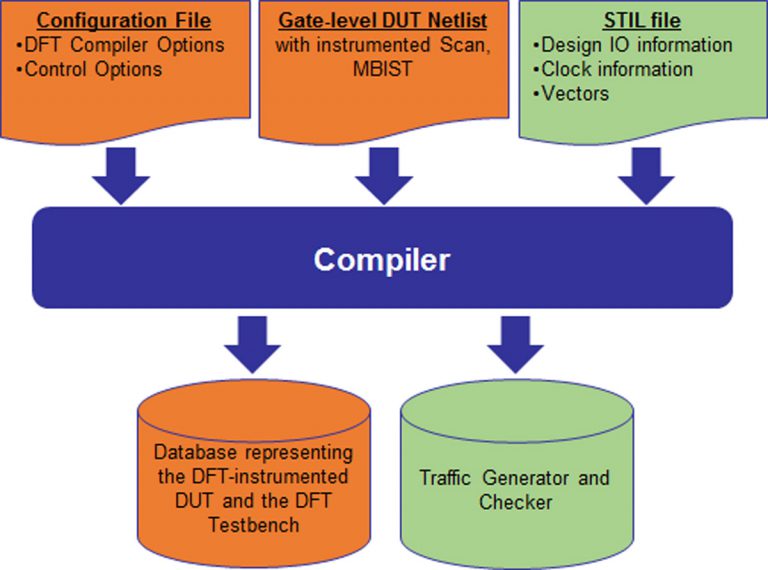

First, a gate-level design instrumented with scan and MBIST is fed into the hardware emulation’s compiler together with an industry-standard STIL format file including design I/O configuration, clock information, and test vectors.

The compiler creates the necessary infrastructure for reading test vectors from the STIL file, namely, a traffic generator and checker, synthesizes the DUT gate-level netlist inclusive of the DFT logic into a structural description compatible with emulation, and generates the DFT testbench. The test logic also comprises a mechanism to compare the DUT’s outputs (Figure 1).

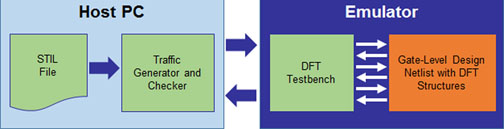

At invocation time, design and testbench are mapped into the emulator. During runtime, the emulator reads the test vectors from the STIL file via the traffic generator created by the compiler and running in the host PC, and applies them via the testbench to the synthesized DUT. The checker compares the DUT’s outputs at emulation speed (Figure 2).

Figure 2. Runtime diagram showing the breakdown of operation in the host PC and emulator

The DFT app enables execution of complete pattern sets for DFT verification to shorten the pattern development cycle. A scalable emulation platform that can accommodate designs of up to a couple of billion gates together with a compiler that can support a DFT methodology empower test-pattern validation for very large gate-level designs with scan and other test structures embedded into them. The DFT app is interoperable with other tools through the standard STIL format file.

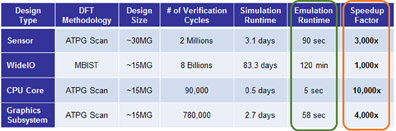

Table 1 summarizes the performance improvement obtained with a modern best-in-class hardware emulator compared with simulation.

An emulation session provides enough verification power to keep the DFT schedule on track, accelerating time to market, increasing yield and boosting profits. Offering a DFT app for hardware emulation broadens the use model, improves performance and helps a verification engineer avoid risk.

Author’s note

*In February, Mentor Graphics, in what it called a new era of hardware emulation, announced new apps for its Veloce emulation platform, including one for DFT. The other apps in the announcement are deterministic in-circuit emulation (ICE) and FastPath, a way to optimize emulation performance when verifying large multi-clock SoC designs by enabling faster model execution speed. A previously announced app supports low power. Apps are meant to emphasize productivity by making emulation accessible to all types of verification engineers without requiring expertise on the nuances of emulation. They also accelerate many verification tasks that were previously tough to solve, and help verification teams reduce verification risks.